Basit bir J-K flip flop deneyelim dedik, olanlara bak. ![]()

Proteusta bazı komponentler analog ve dijital olarak ayarlanabiliyor. Neye göre ayarlamamız gerekiyor. Bazen devremiz çalışmıyor ya da istenen şekilde çalışmıyor. Bakıyorsunuz şemada sorun yok, fakat devre saçmalıyor.

Bu durumda bazı ayarlamaların yapılması gerektiğine inanıp, ne olduğunu bilmesek de ayarlamalar yapıyoruz. Devre çalışırsa ne ala, ya çalışmazsa. Başka yollar deniyoruz ya da başka simulatörler.

Tam da bu şekilde oldu. Bol miktarda zamanımı çaldı.

Geçenlerde bir arkadaşın sorusu üzerine, iyi olduğumu düşündüğüm lojik kapı sistemlerinde, yardımcı olmak istedim. İnternette zaten denenmiş şemalar var. Fakat proteusta çalışmıyor.

Şemaların hepsi yanlış da, proteus mu doğru olacak dedim. Başka simulatörlerle denemeler yaptım. Hepsi aynı çalışmayı sergileyince, hata yaptığımı düşünmeye başladım.

Tabii ki bu arada soruyu soran arkadaşla da paslaşıyoruz.

Proteusta zaman zaman devrede bulunan bazı komponentlerin, analog dijital ayarlarını değiştiririm. Bu şekilde yapmayı düşündüm.

Fakat devre, lojik kapı devresi. Yani tamamen dijital bir devre. Bu devrede entegreden başka komponent de yok. Bunu neden yapayım dedim.

( Bazen bu tip mantıksız şeyleri denemek de fayda var. O an mantıksız gibi görünse de sonradan mantıklı açıklaması olduğunu görebiliyoruz. )

Dijital bir devre ve bu devrenin sonucu dijital olmalı. Analoğun burada işi ne derken. Dijital devrelerde entegrelerin çalışma sistemini hatırladım. Mesela bazı entegreler 5V luk besleme geriliminde 3,5V üzerini 1 seviyesi olarak kabul ediyor. 1V un altını ise 0 seviyesi olarak kabul ediyor. Sistem hesaplarken bu şekilde düşündüğünde anlık gerilim 3,5 olmayabiliyor. Bu kez sapıtma başlıyor.

Bunun sebebi ise aşağıdaki devrede göreceğiniz üzere çıkıştan girişe yapılan geri besleme giriş uçları. Bir anda 1 oluyor ve bir anda diğer çıkışlarda değişince ters geri besleme hızlı bir şekilde 1 ve 0 olarak değişiyor bu da gerilimin 3,5V ta yükselemeden çalışmasını sağlıyor. Tabii ki bu kez de sapıtmaya başlıyor.

Bu durumu düşünerek bende çıkış kapılarını analog olarak değiştirdim. Bu şekilde çözümün bir kısmı sağlandı. Devre çalışmaya başladı.

Fakat gerçek J-K F/F entegresini lojik kapı devreleriyle simüle etmeye çalıştığımızdan sadece bir kısmı çalışıyor TOGGLE çalışmayı yapamıyordu. Soruyu soran arkadaş ta aynı mantıkla ön kısmını düzeltince Devre istendiği gibi çalışmaya başladı.

Zaman içerisinde bu tip sorunlar yaşandığını bildiğimden, ben de sizlerle paylaşmak istedim.

Bir başka sayfada yine benzer soru sorulmuş ve verilen cevap aşağıdadır.

Analog simülasyon digital simülasyondan çok daha fazla hesap yoğunluğuna sahiptir. Tamamen dijital bir sistem kurduysanız, tüm komponentleri dijital ayarlayın. Simülasyon daha hızlı çalışacaktır.

Şunu da söylemeliyim, Blink gibi program yapıldıysa sadece led yanıp sönüyorsa bu dijital olarak kabul edilir. Fakat PWM denemesi yapıp ledi yavaş yavaş yakıp söndürecekseniz, direnç ve led’i ANALOG olarak ayarlamanızı tavsiye ederim.

Gerçek devrede bu fark etmeyecektir. Gerçek devrede her şey analog gelişir. Sadece entegreler kendi kabulleri doğrultusunda giriş kabul ederler. Çıkışları daima dijital seviyededir.

Bazen de şunu söylüyoruz. Proteusta çalışıyor gerçek devrede çalışmıyor.

Bunun sebebi farklı farklıdır. Bunlardan en önemlisi proteusta entegrelerin VCC GND si kendi içinden bağlandığı için pcb hazırlarken VCC ve GND yi nereye bağlayacağını soran var.

Ayrıca proteusta kristal seçimi yapılıyor kristal kullanılmıyor. Devreniz çalışıyor. Gerçek devre çiziminde kristal yeri ayırmayan kişiler bulunmakta. Bir keresinde ben de bunu yapmıştım kristali sonradan eklemek zorunda kalmıştım.

Bir de tabii ki proteus üzerinde hesaplanırken her şey çok güzel gidiyor sanılıyor. Fakat bazı kabuller kullanılıyor. Gerçek devrede bu kabuller yok. Hata varsa ortaya çıkıyor.

Bir de bu analog dijital meselsi bizi yanıltabilir. Siz devreyi digital olarak çalıştırdınız. Fakat giriş geriliminiz gerçek devrede azaldı dolayısıyla devre sapıtıyor. Bu da gerçek devre ile proteusun arasındaki farktır. Bazen çekilen akımdan dolayı besleme gerilimi düşebiliyor, ayrıca kullandığınız kablo uzunsa ve uygun değil ise gerilim düşüyor. Bu çalışmanızı etkileyebilecektir.

Konumuza dönersek aşağıda gördüğünüz devre J-K Flip Flop devresinin lojik kapılarla yapılmış karşılığıdır. Detaylı bilgi için bu sayfaya bakabilirsiniz.

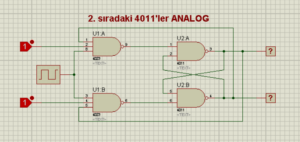

Bu devreyi proteusta kurdum. Tabii ki devre dijital diye dijital olarak kurdum. Sonrasında Çıkıştaki kapı devrelerini ANALOG modunda çalıştırmak zorunda kaldım. Çünkü çıkıştan geriye doğru bir giriş yapılması gerekirken değer dijital çalışmada 5V olması gerekirken 2.5V civarına düşüyordu. bu da 1 seviyesinden az olduğundan çıkış ucu sapıtıyordu. Daha önce dediğimiz gibi 5V luk devreler için 3,5V 1= high seviyesi olarak kabul ediliyor. ANALOG hesaplamada daha detaylı olduğu için bu gerilimin yüksek olduğu ortaya çıkıyor. Gerçek devrede zaten çalışıyor.

Proteusta yapılan ilk devre şeması aşağıdadır. Bu devrede Toogle çalışma hariç gerçekleme tablosu doğrulanıyordu. Sadece Toogle çalışmıyordu.

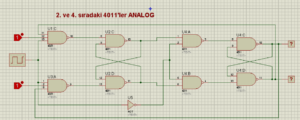

Bunun için ise soruyu soran arkadaş, Master-Slave JK Flip Flop çalışmasından esinlenerek aşağıdaki devreyi denemiş. Tabii ki ilk hali gibi, ÇIKIŞ KAPI larını ANALOG yaparak başarı sağlamış. Aşağıdaki devre ise bu şekilde çalışmasını sağlıyor. Burada toogle çalışmasınıda görebiliyorsunuz.

Resim üzerinde gördüğünüz gibi ANALOG olarak ayarlanan kapılar çıkıştan girişi tetikleyen kapılardır.

Bu detayları videoda görebileceksiniz. Tabii ki videoda bir de şunu göreceksiniz. NAND kapılarıyla bu devreler oluşturuldu. 2 girişli NAND kapısı cmos olarak 4011 kullanıldı. Bunu TTL serisi 74LS38 entegresiyle de oluşturabiliriz. Fakat 74LS38 de ANALOG – DIGITAL ayarı yok. Yani bazı entegrelerde ANALOG – DIGITAL ayarı var. Bazılarında yoktur. Bu şekilde bir değişiklik gerekirse ANALOG – DIGITAL ayarı olan bir entegre ile simülasyonu yapıp sonrasında gerçekte kendi entegrenizi kullanabilirsiniz.

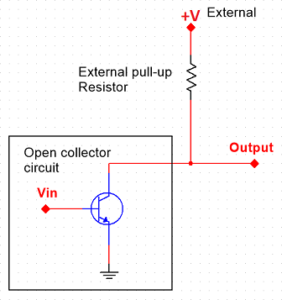

Ayrıca bazı entegreler open collector denilen, kollektörü açık transistörler ile çıkış yaparlar. 74LS38 böyle bir entegre. Bu tip çıkışı olan entegrelerin çalışması için çıkışlarına pull up direnç koymamız gerekiyor. Başka türlü gerekli çıkışı alamazsınız.

Open kollektör çıkışı nasıl olur derseniz, durum bu resimde gösterildiği gibidir. Transistörün bulunduğu yer kapı devresinin çıkışını temsil ediyor. Biz ise pull up direncini ek olarak koyuyoruz.

Bu durum videoda gösterilmektedir.

Soruyu soran ve devrenin son şeklini veren arkadaş : Yusuf Baran kendisine katkıları için teşekkürler.

Sizler de proteus denemeleriniz sırasında bu tip problemlerle karşılaştıysanız bunları yorum bölümünde bizimle paylaşabilirsiniz.

Mantık devrelerinde iyi olduğunuzdan bahsetmişsiniz. Mantık kapılarında (statik mantık kapıları ya da ardışıl mantık elemanlarında -flipfloplar ve bunlardan oluşan sayıcılar, bölücüler vs.-) fonksiyonel anlamda aynı işlevleri yerine getirirler ancak yarıiletken yapı ve elektriksel özellikler anlamında birbirlerinden oldukça farklıdırlar. Bazen çok basit devrelerde dahi birbirlerinin yerine kullanılamazlar. Temelde TTL ve CMOS olarak ayrılırlar ama bunların içerisinde de alt gruplar mevcuttur. Kapı gecikmesi/çalışma hızı ve sinyal kondisyonu (0 ve 1 seviyelerine karşılık gelen gerilim seviyeleri), giriş ve çıkış devresinin empedansı -ki bu fanout değerini belirler-, gerilim yükselme hızı (slew rate) gibi mantık devreleri tasarlarken mutlaka dikkate alınması gereken önemli faktörler vardır. Kısacası aslında mantık kapısı dediğimiz ve 0/1 ile çalıştığını varsaydığımız (!) devreler basbayağı bildiğiniz analog devrelerdir. 0 ve 1 mantık seviyelerine karşılık gelen gerilim değerleri ve arada kalan kararsız bölge vardır. 70’li yıllarda ortaya çıkan 74 serisi TTL’ler için genel kabul 0,8V ‘un altındaki gerilimlerin mantık 0 ve 2,4V’un üzerindeki gerilimlerin mantık 1 seviyesi olduğu şeklindedir. Aradaki bölgede kapının nasıl davranacağını kestirmek genellikle mümkün değildir. Modern devrelerde 3,3V hatta 2,2V ile çalışan mantık devreleri mevcuttur. Bunlar içşn bazı tanımları gözden geçirmek gerekir. Genel olarak level translator’ın Türkçe karşılığı olan seviye dönüştürücü devreler ile farklı besleme gerilimleri ile çalışan familyaların birlikte çalışması sağlanır. Özellikle dirençli gerilim bölücülerle gerçeklenen 5V > 3,3V dönüştürücüleri çoğumuz biliriz. CMOS olarak bilinen 4000 serisi familyada ve türevlerinde ise besleme gerilimi aralığı 3V’dan başlayıp 18V’a kadar gidebilmektedir. Hal böyle olunca mantık 0 ve 1 seviyelerine karşılık düşen gerilimler için net değerler verebilmek mümkün olmaz. Ancak besleme geriliminin yüzdesi cinsinden ifade edilen bağıl değerler mevcuttur. Örneğin 4081 CMOS ve kapısında 5V besleme gerilimi için mantık 1 seviyesi olarak kabul edilen en düşük gerilim 3,5V’tur. Bu aslında şu duruma işaret etmektedir: CMOS yapıda kararsız bölge (analog bölge) oldukça geniştir. O kadar ki CMOS mantık devreleri uygun öngerilim (bias) ve geribesleme (feedback) koşullarında analog yükseltici olarak kullanılabilir. Ben denedim ve gayet iyi çalışıyorlar. Eskilerden bildiğimiz National Semiconductor firmasının bu konuyla ilgili ilginç bir uygulama notu dahi mevcuttur. Yani simülasyon programlarında CMOS yapıdaki mantık kapılarının çıkışlarını analof olarak tanımlamanıza izin verilmesinin sebebi budur. CMOS kapılar yükselme ve düşme hızı yeterince yüksek olmayan sinyalleri sevmezler. Çünkü bu 0 ve 1 seviyeleri arasındaki kararsız bölgede uzun süre kalmak anlamına gelir ve girişi hızlı bir şekilde takip etmesi gereken çıkış kararsız durumda kalarak iterasyonla durum tespiti yapan simülasyon programını saçmalatır.

Degerli bilgiler icin tesekkurler. Soyledikleriniz bana ve kullanicilara faydali olacaktir. Dediginiz gibi dijital sistem olarak degerlendirsek de maalesef hepsinin calisma sartlari gercekte analogtur. Sapitmamasi icin bazi sartlarin gerceklesmesi lazim. Zaman icerisinde bu tip devreleri kullanirken ( mikroislemciletden once ) bir cok sorunla karsilastim. Bir kismi besleme sorunlari olsa da zamanlama sorunlari ozellikle cmoslarda cok basima geldi bazen kondansator destekli calistirmak zorunda kaldim, bazen de zener kullanarak sorunlari cozmeye calistim. Tabii ki seneler sonra cikan yeni entegreler daha stabildir. Ozellille ttl serisinin daha stabil oldugunu dusunuyorum. Proteus ta bu tip sorunlarin olmasi bize datasheet okumanin onemini de gosteriyor. Soylediginiz high low gerilim degerleri ve tepkime sureleri burada acikca yaziyor. Tabii ki sorunlarla bogusarak tecrube kazanacagiz desek de herseyi arduino diye dusunen genclerin bu tip devrelerle bakis acilarini genisletmeleri gerekiyor.